Danas postoje dvije najpopularnije procesorske arhitekture. Riječ je o x86, koji je razvijen još 80-ih godina i koristi se u osobnim računalima i ARM-u, koji je moderniji, što omogućuje da procesori budu manji i ekonomičniji. Koristi se u većini mobilnih uređaja ili tableta.

Obje arhitekture imaju svoje prednosti i nedostatke, kao i područja primjene, ali postoje i zajedničke značajke. Mnogi stručnjaci kažu da je ARM budućnost, ali ipak ima neke nedostatke koje x86 nema. U našem današnjem članku ćemo pogledati kako se arm arhitektura razlikuje od x86. Pogledajmo temeljne razlike između ARM-a i x86, a također pokušajmo odrediti što je bolje.

Što je arhitektura?

Procesor je glavna komponenta svakog računalnog uređaja, bilo da se radi o pametnom telefonu ili računalu. Njegova izvedba određuje koliko će brzo uređaj raditi i koliko dugo može raditi na baterijsko napajanje. Jednostavno rečeno, procesorska arhitektura je skup instrukcija koje se mogu koristiti za sastavljanje programa i implementiraju se u hardver koristeći specifične kombinacije procesorskih tranzistora. Oni omogućuju programima interakciju s hardverom i određuju kako će se podaci prenijeti u memoriju i čitati iz memorije.

Na ovaj trenutak Postoje dvije vrste arhitektura: CISC (Complex Instruction Set Computing) i RISC (Reduced Instruction Set Computing). Prvi pretpostavlja da će procesor implementirati upute za sve prilike, drugi, RISC, postavlja programerima zadatak stvaranja procesora sa skupom minimalnih instrukcija potrebnih za rad. RISC upute su manje i jednostavnije.

x86 arhitektura

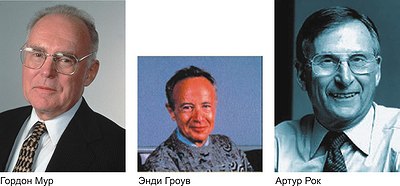

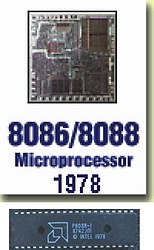

Arhitektura procesora x86 razvijena je 1978. godine i prvi put se pojavila u Intelovim procesorima i tipa je CISC. Ime mu je preuzeto od modela prvog procesora s ovom arhitekturom - Intel 8086. Tijekom vremena, zbog nedostatka najbolja alternativa Drugi proizvođači procesora, poput AMD-a, također su počeli podržavati ovu arhitekturu. To je sada standard za desktop računala, prijenosna računala, netbook računala, poslužitelji i drugi slični uređaji. Ali ponekad se x86 procesori koriste u tabletima, to je prilično uobičajena praksa.

Prvi procesor Intel 8086 imao je 16-bitni kapacitet, zatim je 2000. godine izašao procesor s 32-bitnom arhitekturom, a još kasnije se pojavila 64-bitna arhitektura. O tome smo detaljno raspravljali u zasebnom članku. Tijekom tog vremena, arhitektura se jako razvila; dodani su novi skupovi instrukcija i proširenja, što može znatno povećati performanse procesora.

x86 ima nekoliko značajnih nedostataka. Prvo, to je složenost naredbi, njihova zamršenost, koja je nastala zbog duge povijesti razvoja. Drugo, takvi procesori troše previše energije i zbog toga stvaraju puno topline. x86 inženjeri u početku su krenuli putem postizanja maksimalnih performansi, a brzina zahtijeva resurse. Prije nego što pogledamo razlike između arm x86, razgovarajmo o ARM arhitekturi.

ARM arhitektura

Ova arhitektura je predstavljena nešto kasnije iza x86 - 1985. godine. Razvila ju je poznata britanska tvrtka Acorn, tada se ta arhitektura zvala Arcon Risk Machine i pripadala je tipu RISC, no tada je izašla njena poboljšana verzija Advanted RISC Machine, koja je danas poznata kao ARM.

Prilikom razvoja ove arhitekture inženjeri su si postavili cilj otkloniti sve nedostatke x86 i stvoriti potpuno novu i najučinkovitiju arhitekturu. ARM čipovi imali su minimalnu potrošnju energije i nisku cijenu, ali su imali niske performanse u usporedbi s x86, tako da u početku nisu stekli veliku popularnost na osobnim računalima.

Za razliku od x86, programeri su u početku pokušali dobiti minimalni troškovi na resursima, imaju manje procesorskih instrukcija, manje tranzistora, ali i, sukladno tome, manje svih vrsta dodatne mogućnosti. Ali performanse ARM procesora se posljednjih godina poboljšavaju. S obzirom na to i malu potrošnju energije, počeli su se vrlo široko koristiti u Mobilni uredaji, kao što su tableti i pametni telefoni.

Razlike između ARM i x86

A sada kada smo pogledali povijest razvoja ovih arhitektura i njihove temeljne razlike, napravimo detaljnu usporedbu ARM-a i x86 na temelju njihovih različitih karakteristika kako bismo utvrdili koja je bolja i točnije razumjeli njihove razlike.

Proizvodnja

Proizvodnja x86 u odnosu na arm je drugačija. Samo dvije tvrtke proizvode x86 procesore: Intel i AMD. U početku je to bila jedna tvrtka, ali to je sasvim druga priča. Samo te tvrtke imaju pravo proizvoditi takve procesore, što znači da će samo one kontrolirati smjer razvoja infrastrukture.

ARM radi vrlo drugačije. Tvrtka koja razvija ARM ne izdaje ništa. Oni jednostavno izdaju dopuštenje za razvoj procesora ove arhitekture, a proizvođači mogu raditi što god žele, na primjer, proizvoditi određene čipove s modulima koji im trebaju.

Broj uputa

Ovo su glavne razlike između arm i x86 arhitekture. x86 procesori su se brzo razvijali kao moćniji i produktivniji. Dodali su programeri veliki broj procesorske upute, a ovdje nema samo osnovnog skupa, već dosta naredbi koje se mogu izostaviti. U početku je to učinjeno kako bi se smanjila količina memorije koju zauzimaju programi na disku. Također su razvijene mnoge opcije za zaštitu i virtualizaciju, optimizaciju i još mnogo toga. Sve to zahtijeva dodatne tranzistore i energiju.

ARM je jednostavniji. Ovdje ima puno manje instrukcija procesora, samo onih koje operacijski sustav treba i koje se stvarno koriste. Ako usporedimo x86, onda se tamo koristi samo 30% svih mogućih instrukcija. Lakše ih je naučiti ako se odlučite ručno pisati programe, a također zahtijevaju manje tranzistora za implementaciju.

Potrošnja energije

Još jedan zaključak proizlazi iz prethodnog paragrafa. Što je više tranzistora na pločici, veća je njena površina i potrošnja energije, a vrijedi i obrnuto.

x86 procesori troše puno više energije nego ARM. Ali na potrošnju energije utječe i veličina samog tranzistora. Na primjer, procesor Intel i7 troši 47 vata, a bilo koji procesor pametnog telefona ARM ne troši više od 3 vata. Prethodno su se proizvodile ploče s veličinom jednog elementa od 80 nm, zatim je Intel postigao smanjenje na 22 nm, a ove godine znanstvenici su uspjeli stvoriti ploču s veličinom elementa od 1 nanometar. To će uvelike smanjiti potrošnju energije bez gubitka performansi.

Posljednjih godina, potrošnja energije x86 procesora se jako smanjila, na primjer, novih procesora Intel Haswell može duže trajati na baterije. Sada razlika između arma i x86 postupno nestaje.

Odvođenje topline

Broj tranzistora utječe na još jedan parametar - stvaranje topline. Moderni uređaji ne može pretvoriti svu energiju u učinkovito djelovanje; dio se raspršuje u obliku topline. Učinkovitost ploča je ista, što znači da što je manje tranzistora i što je njihova veličina manja, to će procesor stvarati manje topline. Ovdje se više ne postavlja pitanje hoće li ARM ili x86 generirati manje topline.

Performanse procesora

ARM nije izvorno dizajniran za maksimalnu izvedbu, ovdje se x86 ističe. Djelomično je to zbog manjeg broja tranzistora. Ali u posljednje vrijeme performanse ARM procesora su u porastu i oni se već mogu u potpunosti koristiti u prijenosnim računalima ili poslužiteljima.

zaključke

U ovom smo članku pogledali kako se ARM razlikuje od x86. Razlike su prilično ozbiljne. Ali u posljednje vrijeme granica između obje arhitekture postala je nejasna. ARM procesori postaju sve produktivniji i brži, a x86 procesori, zahvaljujući smanjenju veličine strukturnog elementa ploče, počinju trošiti manje energije i generirati manje topline. ARM procesore već možete pronaći na poslužiteljima i prijenosnim računalima, a x86 na tabletima i pametnim telefonima.

Što mislite o ovim x86 i ARM-u? Koja je tehnologija budućnost po vašem mišljenju? Pišite u komentarima! Usput, .

Za kraj videa o razvoju ARM arhitekture:

Glavne značajke arhitekture

SSE4 se sastoji od 54 instrukcije, od kojih je 47 klasificirano kao SSE4.1 (nalaze se samo u Penryn procesorima). Kompletan set instrukcija (SSE4.1 i SSE4.2, tj. 47 + preostalih 7 instrukcija) dostupan je u Nehalem procesorima. Nijedna od SSE4 instrukcija ne radi sa 64-bitnim mmx registrima, samo sa 128-bitnim xmm0-15. Nisu objavljeni 32-bitni procesori sa SSE4.

Dodane upute koje ubrzavaju kompenzaciju pokreta u video kodecima, brzo čitanje iz USWC memorije i mnoge upute za pojednostavljenje vektorizacije programa od strane prevoditelja. Dodatno, SSE4.2 je dodao upute za obradu nizova od 8/16 bitnih znakova, izračunavanje CRC32, popcnt. Po prvi put u SSE4, registar xmm0 korišten je kao implicitni argument za neke instrukcije.

Nove instrukcije SSE4.1 uključuju video akceleraciju, vektorske primitive, umetanje/ekstrakciju, vektorsko skalarno množenje, miješanje, provjeru bitova, zaokruživanje i čitanje WC memorije.

Nove instrukcije SSE4.2 uključuju obradu nizova, CRC32 brojanje, jednobitno brojanje populacije i rad s vektorskim primitivima.

SSE5

Novo x86 proširenje instrukcija iz AMD-a pod nazivom SSE5. Ovaj potpuno novi skup SSE instrukcija, kreiran od strane AMD stručnjaka, podržavat će obećavajuće CPU tvrtke počevši od 2009. godine.

SSE5 klasičnoj x86 arhitekturi donosi neke značajke koje su prethodno bile dostupne isključivo u RISC procesorima. Skup instrukcija SSE5 definira 47 novih osnovnih instrukcija dizajniranih da ubrzaju jednonitno računalstvo povećanjem gustoće obrađenih podataka.

Među novim uputama ističu se dvije glavne skupine. Prvi uključuje upute koje akumuliraju rezultate množenja. Ove vrste uputa mogu biti korisne za organiziranje iterativnih računalnih procesa prilikom renderiranja slika ili stvaranja 3D audio efekata. U drugu skupinu novih instrukcija spadaju instrukcije koje rade na dva registra i pohranjuju rezultat u treći. Ova bi inovacija mogla programerima omogućiti izbjegavanje nepotrebnih prijenosa podataka između registara u računalnim algoritmima. SSE5 također sadrži nekoliko novih uputa za usporedbu vektora, za preuređivanje i premještanje podataka, kao i za promjenu preciznosti i zaokruživanje.

AMD vidi računalne zadatke, obradu multimedijskog sadržaja i alate za šifriranje kao glavne aplikacije za SSE5. Očekuje se da u računalnim aplikacijama koje koriste matrične operacije korištenje SSE5 može pružiti povećanje performansi od 30%. Multimedijski zadaci koji zahtijevaju performanse diskretne kosinusne transformacije mogu imati koristi od 20% ubrzanja. A algoritmi šifriranja zahvaljujući SSE5 mogu postići peterostruko povećanje brzine obrade podataka.

AVX

Sljedeći set proširenja je od Intela. Podržana je obrada brojeva s pomičnim zarezom pakiranih u 256-bitne "riječi". Za njih je uvedena podrška za iste naredbe kao u SSE obitelji. 128-bitni SSE registri XMM0 - XMM15 proširuju se na 256-bitni YMM0-YMM15

Procesorska proširenja Intel Post 32nm novi su skup Intelovih instrukcija koje vam omogućuju pretvaranje brojeva polovične preciznosti u brojeve jednostruke i dvostruke preciznosti, dobivanje stvarnih nasumičnih brojeva u hardveru i pristup FS/GS registrima.

AVX2

Daljnji razvoj AVX-a. SSE integer upute počinju raditi s 256-bitnim AVX registrima.

AES

Proširenje skupa AES instrukcija—mikroprocesorska implementacija AES enkripcije.

3DNow!

Skup instrukcija za obradu toka realnih brojeva jednostruke preciznosti. Podržavaju AMD procesori počevši od K6-2. Ne podržavaju Intel procesori.

Upute 3DNow! koristite MMX registre kao operande (dva broja pojedinačne preciznosti smještena su u jedan registar), tako da, za razliku od SSE-a, nema potrebe posebno spremati 3DNow! kontekst prilikom prebacivanja zadataka.

64-bitni način rada

Superskalarno znači da procesor može izvesti više od jedne operacije u jednom taktu. Superpipelinizacija znači da procesor ima više računalnih cjevovoda. Pentium ih ima dva, što mu omogućuje da, na istim frekvencijama, idealno bude dvostruko produktivniji od 486, izvršavajući 2 instrukcije po taktu.

Osim toga, značajka Pentium procesora bila je potpuno redizajnirana i za to vrijeme vrlo moćna FPU jedinica čije su performanse ostale nedostižne konkurenciji sve do kraja 1990-ih.

Pentium OverDrive

Osim toga, jezgri Pentiuma II dodan je MMX blok.

Celeron

Prvi predstavnik ove obitelji temeljio se na arhitekturi Pentium II; bio je to uložak s tiskanom pločicom na kojoj su bili montirani jezgra, predmemorija druge razine i oznaka predmemorije. Montira se u utor 2.

Moderni Xeoni temelje se na arhitekturi Core 2/Core i7.

AMD procesori

Am8086 / Am8088 / Am186 / Am286 / Am386 / Am486Temeljno novo AMD procesor(travanj 1997.), temeljen na kernelu kupljenom od NexGena. Ovaj procesor imao je dizajn pete generacije, ali je pripadao šestoj generaciji i bio je pozicioniran kao konkurent Pentiumu II. Uključuje MMX blok i blago redizajnirani FPU blok. Međutim, ti su blokovi i dalje radili 15-20% sporije od onih sličnih frekvencija Intel procesori. Procesor je imao 64 KB L1 predmemorije.

Općenito, performanse usporedive s Pentiumom II, kompatibilnost sa starijim matičnim pločama, ranije lansiranje (AMD je predstavio K6 mjesec dana ranije nego što je Intel predstavio P-II) i niža cijena učinili su ga prilično popularnim, ali AMD-ovi proizvodni problemi značajno su pokvarili reputaciju ovog procesora.

K6-2Daljnji razvoj jezgre K6. Ovi procesori dodali su podršku za specijalizirani 3DNow! . Međutim, ispostavilo se da je stvarna izvedba znatno niža od one kod Pentiuma II sa sličnim taktom (to je zbog činjenice da je povećanje performansi s povećanjem frekvencije u P-II bilo veće zbog unutarnje predmemorije) i K6-2 je mogao konkurirati samo Celeronu. Procesor je imao 64 KB L1 predmemorije.

K6-IIITehnološki uspješniji od K6-2, pokušaj stvaranja analoga Pentiuma III. Međutim, to nije bio marketinški uspjeh. Ističe se prisutnošću 64 KB predmemorije prve razine i 256 KB predmemorije druge razine u jezgri, što mu je omogućilo da nadmaši Intel Celeron na istoj taktnoj frekvenciji i ne bude značajno inferiorniji od ranog Pentiuma III. .

K6-III+Analogni K6-III s tehnologijom uštede energije PowerNow! i više visoka frekvencija i proširen skup uputa. Izvorno namijenjen za prijenosna računala. Također je instaliran u stolnim sustavima sa Super 7 procesorskom utičnicom. Koristi se za nadogradnju stolnih sustava s procesorskom utičnicom Socket 7 (Samo na matičnim pločama koje opskrbljuju procesor s dva napona napajanja, prvim za I/O jedinice procesora i drugim za jezgru procesora. Nisu svi proizvođači osigurali dvostruko napajanje na prvi modeli njihovih matičnih ploča s utičnicom Socket 7).

Analogno K6-III+ s predmemorijom druge razine smanjenom na 128 KB.

AthlonVrlo uspješan procesor, zahvaljujući kojem je AMD uspio vratiti gotovo izgubljene pozicije na tržištu mikroprocesora. Predmemorija prve razine - 128 KB. U početku se procesor proizvodio u kazeti s predmemorijom druge razine (512 KB) smještenoj na ploči i instaliranoj u utoru A (koji je mehanički, ali nije električni kompatibilan s utorom 1 od Intela). Zatim sam se prebacio na Socket A i imao 256 KB predmemorije druge razine u jezgri. Što se tiče performansi - približan analog Pentiuma III.

DuronSkraćena verzija Athlona, razlikuje se od svog roditelja po veličini predmemorije druge razine (samo 64 KB, ali integrirana u čip i radi na frekvenciji jezgre).

Konkurent Celeron generacijama Pentiuma III / Pentiuma 4. Performanse su osjetno veće od onih sličnih Celerona i odgovaraju Pentiumu III pri obavljanju mnogih zadataka.

Athlon XPNastavak razvoja Athlon arhitekture. Što se tiče performansi, sličan je Pentiumu 4. U usporedbi s običnim Athlonom, dodana je podrška za SSE upute.

SempronJeftinija (zbog smanjene predmemorije druge razine) verzija procesora Athlon XP i Athlon 64.

Prvi Sempronovi modeli bili su preimenovani u Athlon XP čipove na Thoroughbred i Thorton jezgri, koji su imali 256 KB predmemorije druge razine i radili na 166 (333 DDR) sabirnici. Kasnije su smanjene verzije Athlona 64/Athlona II proizvedene (i jesu) pod markom Sempron, pozicionirane kao konkurencija Intel Celeronu. Svi Semproni imaju smanjenu predmemoriju razine 2; mlađi Socket 754 modeli su blokirali Cool&quiet i x86-64; Socket 939 modeli imali su zaključani dvokanalni način rada memorije.

OpteronPrvi procesor koji podržava x86-64 arhitekturu.

Athlon 64Prvi ne-poslužiteljski procesor koji podržava x86-64 arhitekturu.

Athlon 64 X2Nastavak arhitekture Athlon 64, ima 2 računalne jezgre.

Athlon FX

Bio je na glasu kao "najviše brzi procesor za igračke." Je li, zapravo, poslužiteljski procesor Opteron 1xx na stolnim utičnicama bez podrške za registriranu memoriju. Proizvodi se u malim serijama. Košta znatno više od svojih "masovnih" kolega.

PhenomDaljnji razvoj arhitekture Athlon 64, dostupan je u verzijama s dvije (Athlon 64 X2 Kuma), tri (Phenom X3 Toliman) i četiri (Phenom X4 Agena) jezgre.

Fenom IIVIA procesori

Cyrix III/VIA C3Prvi procesor izdan pod markom VIA. Izdano s različitim kernelima različitih razvojnih timova. Socket 370 konektor.

Prvo izdanje temelji se na Joshua kernelu, koji je VIA dobila zajedno s razvojnim timom Cyrixa.

Drugo izdanje je s jezgrom Samuel, razvijenom na temelju nikada objavljenog IDT WinChip -3. Odlikuje ga odsutnost predmemorije druge razine i, sukladno tome, izuzetno niska razina performansi.

Treće izdanje je s jezgrom Samuel-2, poboljšanom verzijom prethodne jezgre, opremljenom predmemorijom druge razine. Procesor je proizveden tanjom tehnologijom i imao je smanjenu potrošnju energije. Nakon izdavanja ove jezgre, marka “VIA Cyrix III” konačno je ustupila mjesto “VIA C3”.

Četvrto izdanje je s jezgrom Ezra. Postojala je i varijanta Ezra-T, prilagođena za rad na sabirnici dizajniranoj za Intelove procesore s jezgrom Tualatin. Daljnji razvoj u smjeru uštede energije.

Peto izdanje je s jezgrom Nehemiah (C5P). Ova je jezgra konačno dobila koprocesor pune brzine, podršku za upute ili .

Procesori temeljeni na V33 jezgri nisu imali način emulacije 8080, ali su ga podržavali pomoću dva dodatne upute, prošireni način adresiranja.

NexGen procesori

Nx586U ožujku 1994. godine predstavljen je NexGen Nx586 procesor. Bio je postavljen kao konkurent Pentiumu, ali u početku nije imao ugrađeni koprocesor. Korištenje vlastite sabirnice zahtijevalo je korištenje vlastitih skupova čipova, NxVL (VESA lokalna sabirnica) i NxPCI 820C500 (PCI), te nekompatibilnu procesorsku utičnicu. Čipseti su razvijeni zajedno s VLSI i Fujitsu. Nx586 je bio superskalarni procesor i mogao je izvršiti dvije instrukcije po taktu. L1 predmemorija bila je odvojena (16 KB za upute + 16 KB za podatke). L2 cache kontroler bio je integriran u procesor, dok se sam cache nalazio na matična ploča. Baš kao i Pentium Pro, Nx586 je imao RISC procesor. Nedostatak podrške za CPUID instrukcije u ranim modifikacijama ovog procesora doveo je do toga da je softverski definiran kao brzi 386 procesor. Tome je pridonijela i činjenica da se Windows 95 nije htio instalirati na računala s takvim procesorima. Za rješavanje ovog problema korišten je poseban uslužni program (IDON.COM) koji je Nx586 za Windows predstavio kao CPU klase 586. Nx586 je proizveden u IBM pogonima.

Nx587 FPU koprocesor također je razvijen i tvornički montiran na vrhu procesorske matrice. Takvi "sklopovi" su označeni kao Nx586Pf. Prilikom označavanja performansi Nx586 korištena je P-ocjena - od PR75 (70 MHz) do PR120 (111 MHz).

Sljedeća generacija NexGen procesora, koji nikada nisu objavljeni, ali su poslužili kao osnova za AMD K6.

SiS procesori

SiS550Obitelj SiS550 SoC temelji se na licenciranoj jezgri Rise mP6 i dostupna je s frekvencijama od 166 do 266 MHz. Istovremeno, najbrža rješenja troše samo 1,8 W. Jezgra ima tri cjevovoda cjelobrojnih 8 stupnjeva. L1 odvojena predmemorija, 8+8 KB. Ugrađeni koprocesor je cjevovodan. Uz standardni skup priključaka, SiS550 uključuje 128-bitnu UMA video jezgru AGP 4x, 5.1-kanalni audio i podršku za 2-instrukcije pod nazivom Code Morphing Software. To omogućuje procesoru da se prilagodi bilo kojem skupu instrukcija i poboljšava energetsku učinkovitost, no performanse takvog rješenja očito su niže od onih procesora s izvornim x86 sustavom instrukcija. matematički koprocesor, a varijante s koprocesorom trebale su se zvati U5D, ali nikada nisu objavljene.

Intel je dobio sudsku zabranu prodaje Green CPU-a u Sjedinjenim Državama, tvrdeći da je UMC koristio Intelov mikrokod u svojim procesorima bez licence.

Bilo je i problema sa softverom. Na primjer, igra Doom odbila se pokrenuti na ovom procesoru bez promjene konfiguracije, a Windows 95 se s vremena na vrijeme smrzavao. To je bilo zbog činjenice da su programi pronašli nedostajući koprocesor u U5S i pokušaji da mu pristupe završili su neuspjehom.

Procesori proizvedeni u SSSR-u i Rusiji

KR1810VM86BLX IC dizajn/ICT procesori

BLX IC dizajn i institut računalna tehnologija Od 2001. Kina razvija procesore temeljene na MIPS-u s hardverskim prijevodom x86 instrukcija. Ove procesore proizvodi STMicroelectronics. Razmatra se partnerstvo sa TSMC-om.

Kumče (Longxin, Loongson, Zmaj)

Godson je 32-bitni RISC procesor temeljen na MIPS-u. Tehnologija - 180 nm. Predstavljen 2002. godine. Frekvencija - 266 MHz, godinu dana kasnije - verzija s frekvencijom od 500 MHz.

Kumče 2

- Godson 2 je 64-bitni RISC procesor temeljen na MIPS III. 90 nm tehnologija. Na istoj frekvenciji je 10 puta brži od svog prethodnika. Predstavljen 19. travnja 2005.

- Godson-2E - 500 MHz, 750 MHz, kasnije - 1 GHz. Tehnologija - 90 nm. 47 milijuna tranzistora, potrošnja energije - 5 ... 7,5 W. Prvi Godson s hardverskim prijevodom x86 naredbi, a na njega se troši i do 60% performansi procesora. Predstavljen u studenom 2006.

- Godson 2F - 1,2 GHz, proizvodi se od ožujka 2007. Deklarirano je povećanje produktivnosti od 20-30% u usporedbi s prethodnikom.

- Godson 2H - planiran za izlazak 2011. Bit će opremljen ugrađenom video jezgrom i memorijskim kontrolerom te je namijenjen potrošačkim sustavima.

- Godson 3 - 4 jezgre, 65 nm tehnologija. Potrošnja energije je oko 20 W.

- Godson 3B - 8 jezgri, 65 nm tehnologija (planirani prijelaz na 28 nm), radni takt unutar 1 GHz. Površina kristala - 300 mm². Performanse s pomičnim zarezom su 128 GigaFLOPS. Potrošnja energije 8-jezgrenog Godsona je 3-40 W. Prijevod u x86 kod izvodi se pomoću skupa od 200 instrukcija; oko 20% performansi procesora troši se na prijevod. Procesor ima 256-bitnu vektorsku SIMD procesorsku jedinicu. Procesor je namijenjen za korištenje u poslužiteljima i ugrađenim sustavima.

Struktura proizvoljne instrukcije je sljedeća:

- Prefiksi (svaki od njih nije obavezan):

- Jednobajtni prefiks za promjenu načina adresiranja AddressSize (vrijednost 67h).

- Jednobajtni prefiks promjene segmenta (vrijednosti 26h, 2Eh, 36h, 3Eh, 64h i 65h).

- Jednobajtni BranchHint prefiks za označavanje preferirane grane (vrijednosti 2Eh i 3Eh).

- Dvobajtni ili trobajtni složeni Vex prefiks (prvi bajt uvijek ima vrijednost C4h za verziju od dva bajta ili C5h za verziju od tri bajta).

- Jednobajtni prefiks zaključavanja za sprječavanje modifikacije memorije od strane drugih procesora ili jezgri (vrijednost F0h).

- Jednobajtni prefiks OperandsSize za promjenu veličine operanda (vrijednost 66h).

- Jednobajtni Obavezni prefiks za pojašnjenje instrukcije (vrijednosti F2h i F3h).

- Jednobajtni prefiks Repeat znači ponavljanje (vrijednosti F2h i F3h).

- Jednobajtni strukturirani Rex prefiks je potreban za označavanje 64-bitnih ili proširenih registara (ima vrijednosti 40h..4Fh).

- Escape prefiks. Uvijek se sastoji od najmanje jednog bajta 0Fh. Iza ovog bajta po izboru slijedi bajt 38h ili 3Ah. Dizajniran za pojašnjenje uputa.

- Bajtovi koji precizno definiraju instrukciju su:

- Opcode bajt (proizvoljna konstantna vrijednost).

- Opcode2 bajt (proizvoljna konstantna vrijednost).

- Params bajt (ima složenu strukturu).

- ModRm bajt se koristi za operande u memoriji (ima složenu strukturu).

- SIB bajt se također koristi za memorijske operande i ima složenu strukturu.

- Podaci ugrađeni u upute (opcionalno):

- Pomak ili adresa u memoriji. Cijeli broj s predznakom veličine 8, 16, 32 ili 64 bita.

- Prvi ili jedini neposredni operand (Immediate). Može biti veličine 8, 16, 32 ili 64 bita.

- Drugi neposredni operand (Immediate2). Ako postoji, obično je veličine 8 bita.

U gornjem i donjem popisu, za tehničke nazive, prihvaća se naziv "samo latinski, arapski brojevi" i znak minus "-" s podvlakom "_", a velika i mala slova je CamelCase (bilo koja riječ počinje velikim slovom, a zatim samo malim slovima, čak i ako je kratica: “ UTF-8" → "Utf8" - sve riječi zajedno). Prefiksi AddressSize, Segment, BranchHint, Lock, OperandsSize i Repeat mogu se miješati zajedno. Preostali elementi moraju ići točno navedenim redoslijedom. I možete vidjeti da su vrijednosti bajtova nekih prefiksa iste. Njihova svrha i dostupnost određuju se samim uputama. Prefiksi nadjačavanja segmenata mogu se koristiti s većinom uputa, ali prefiksi BranchHint mogu se koristiti samo s uputama uvjetnog grananja. Slična je situacija i s prefiksima Mandatory i Repeat - negdje pojašnjavaju upute, a negdje označavaju ponavljanje. Prefiks OperandSize, zajedno s obaveznim prefiksima, također se klasificiraju kao prefiksi SIMD instrukcija. Zasebno treba reći o prefiksu Vex. Zamjenjuje prefikse Rex, Mandatory, Escape i OperandsSize, zbijajući ih u sebe. Nije dopušteno koristiti prefiks Lock s njim. Sam prefiks zaključavanja može se dodati kada je odredište operand u memoriji.

Pregledni popis svih načina od interesa u smislu kodiranja uputa:

- 16-bitni ("stvarni način rada", stvarni način rada s adresiranjem segmenata).

- 32-bitni ("Protected Mode", zaštićeni način rada s ravnim modelom memorije).

- 64-bitni ("Dugi način rada", poput 32-bitnog zaštićenog s ravnim modelom memorije, ali adrese su već 64-bitne).

U zagradama engleski nazivi modova odgovaraju službenim. Postoje i sintetički modovi kao što je unreal (Unreal x86 Mode), ali svi oni proizlaze iz ova tri (u suštini, to su hibridi koji se razlikuju samo po veličini adrese, operandima itd.). Svaki od njih koristi "nativni" način adresiranja, ali se može promijeniti u alternativni s prefiksom OperandsSize. U 16-bitnom načinu rada bit će omogućen 32-bitni način adresiranja, u 32-bitnom načinu - 16-bitni, au 64-bitnom načinu - 32-bitni. Ali ako to učinite, adresa se proširuje nulama (ako je manja) ili se njeni najvažniji bitovi resetiraju (ako je veća).

4.6. Značajke arhitekture modernih x86 procesora

4.6.1. Arhitektura procesora Intel Pentium(P5/P6)

Procesori obitelji Pentium imaju niz arhitektonskih i strukturalnih značajki u odnosu na prethodne modele Intelovih mikroprocesora. Najkarakterističniji od njih su:

Harvardska arhitektura s odvajanjem tokova naredbi i podataka uvođenjem zasebnih blokova unutarnje predmemorije za pohranu naredbi i podataka, kao i sabirnica za njihov prijenos;

Superskalarna arhitektura, koja osigurava istovremeno izvršavanje nekoliko naredbi u paralelnim operativnim uređajima;

Dinamičko izvršavanje naredbi, koje implementira promjenu niza naredbi, koristeći proširenu datoteku registra (preimenovanje registra) i učinkovito predviđanje grananja;

Dvostruka nezavisna sabirnica koja sadrži zasebnu sabirnicu za pristup L2 predmemorije (koja radi na taktu procesora) i sistemsku sabirnicu za pristup memoriji i vanjski uređaji(radi na taktu matične ploče).

Glavne karakteristike Pentium obitelji procesora su sljedeće:

32-bitna unutarnja struktura;

Korištenje sistemske sabirnice s 36 adresnih bita i 64 podatkovna bita;

Odvojena interna L1 predmemorija za upute i podatke kapaciteta 16 KB;

Podržava dijeljene L2 instrukcije i predmemoriju podataka do 2 MB;

Cjevovodno izvršavanje naredbi;

Predviđanje smjera grananja softvera s visokom točnošću;

Ubrzano izvođenje operacija s pomičnim zarezom;

Kontrola prioriteta pri pristupu memoriji;

Podrška za implementaciju višeprocesorskih sustava;

Dostupnost internih alata koji omogućuju samotestiranje, otklanjanje pogrešaka i praćenje performansi.

Nova mikroarhitektura Pentium procesori (riža. 4.6)a kasnije se temelji na metodi superskalarna obrada .

Pod, ispod superskalarnost podrazumijeva prisutnost više jedan cjevovod za obradu naredbi (za razliku od skalarne - jednocijevne arhitekture).

Slika 4.6 – Blok dijagram arhitekture Pentium MP

U Pentium MP, naredbe su raspoređene preko dva neovisna izvršna cjevovoda (U i V). Transporter U može izvršiti bilo koju IA-32 obitelj naredbi, uključujući naredbe cijelog broja i pomičnog zareza. Pokretna traka V dizajniran za izvršavanje jednostavnih integerskih instrukcija i nekih instrukcija s pomičnim zarezom. Naredbe se mogu slati na svaki od ovih uređaja istovremeno, a kada upravljački uređaj izda par naredbi u jednom taktu, složenija naredba ide u U cjevovod, a manje složena ide u V cjevovod.

Međutim, takva parna obrada naredbi (uparivanje) moguća je samo za ograničeni podskup cjelobrojnih naredbi. Prave aritmetičke instrukcije ne mogu se izvoditi u sprezi s integerima. Istodobno izdavanje dviju naredbi moguće je samo ako ne postoje ovisnosti registra.

Jedna od glavnih značajki šeste generacije mikroprocesora IA-32 arhitekture je dinamičan(spekulativno) izvršenje. Ovaj izraz označava sljedeći skup mogućnosti:

- predviđanje duboke grane(s vjerojatnošću od >90% možete predvidjeti sljedećih 10-15 prijelaza);

- analiza protoka podataka(pogledajte program 20-30 koraka unaprijed i odredite ovisnost naredbi o podacima ili resursima);

- naprijed izvršavanje naredbi(MP P6 može izvršavati naredbe redoslijedom koji se razlikuje od njihovog redoslijeda u programu).

Unutarnja organizacija MP P6 odgovara RISC arhitekturi, dakle blok dohvaćanja instrukcija, čitajući IA-32 tok instrukcija iz L1 predmemorija instrukcija, dekodira ih u niz mikrooperacija. Tijek mikrooperacija spada u međuspremnik za preuređivanje (skup instrukcija). Sadrži i mikrooperacije koje još nisu izvedene i one koje su već izvedene, ali još nisu utjecale na stanje procesora.

Za dekodiranje uputa, tri paralelna dekoder: dva za jednostavne i jedan za složene upute.

Svaka IA-32 instrukcija dekodira se u 1-4 mikrooperacije. Izvode se mikrooperacije pet paralelnih aktuatora: dva za cjelobrojna aritmetika, dva za prava aritmetika I blok memorijskog sučelja. Stoga je moguće izvesti do pet mikrooperacija po taktu.

Blok aktuatora sposobni birati upute iz skupa bilo kojim redoslijedom. Istovremeno, zahvaljujući blok predviđanja grananja moguće je izvršiti instrukcije slijedeći uvjetne grane. Blok redundantnosti stalno prati u bazenu instrukcija one mikrooperacije koje su spremne za izvršenje (izvorni podaci ne ovise o rezultatu drugih neizvršenih instrukcija) i usmjerava ih na slobodni izvršni uređaj odgovarajućeg tipa. Jedan od cjelobrojnih aktuatora dodatno provjerava jesu li predviđanja grana točna. Kada se otkrije pogrešno predviđeno grananje, sve mikrooperacije koje slijede nakon prijelaza uklanjaju se iz skupa i cjevovod naredbi se puni uputama na novoj adresi.

Međusobna ovisnost instrukcija o vrijednosti registara IA-32 arhitekture može zahtijevati čekanje da se registri oslobode. Za rješavanje ovog problema dizajnirani su 40 internih registara opće namjene, koji se koristi u stvarnim izračunima.

Izbriši blok prati rezultat spekulativno izvedenih mikrooperacija. Ako mikrooperacija više ne ovisi o drugim mikrooperacijama, njen rezultat se prenosi u stanje procesora i uklanja se iz međuspremnika za preuređivanje. Blok za brisanje potvrđuje izvršenje instrukcija (do tri mikrooperacije po taktu) redoslijedom kojim se pojavljuju u programu, uzimajući u obzir prekide, iznimke, prijelomne točke i promašaje predviđanja grananja.

Opisana shema prikazana je na sl. 4.7.

Slika 4.7 – Blok dijagram mikroprocesora Pentium Pro

4.6.2. SIMD proširenja MMX-a

Mnogi algoritmi za rad s multimedijskim podacima dopuštaju najjednostavnije elemente paralelizacije, kada se jedna operacija može izvoditi paralelno na nekoliko brojeva. Ovaj pristup se zove SIMD – single-instruction multiple-data (jedna instrukcija – više podataka). Ova tehnologija je prvi put implementirana u P55 generaciji (Pentium MMX mikroprocesor).

MMX (Multi-Media Extension) je SIMD proširenje za tokovnu obradu cjelobrojnih podataka, implementirano na temelju FPU bloka (koristeći FPU registre).

Jedna MMX instrukcija može izvesti aritmetičku ili logičku operaciju na "serijama" cijelih brojeva upakiranih u MMX registre. Na primjer, PADDSB instrukcija dodaje 8 bajtova jednog "paketa" s odgovarajućih osam bajtova drugog paketa, učinkovito izvodeći zbrajanje osam parova brojeva s jednom instrukcijom.

4.6.3. Procesori Pentium Pro, Pentium II, Pentium III

Pentium II procesor kombinira najbolje karakteristike Intel procesora: performanse Pentium Pro procesora i mogućnosti MMX tehnologije. Ova kombinacija osigurava značajno povećanje performansi Pentium II procesora u usporedbi s prethodnim procesorima IA-32 arhitekture.

Procesor sadrži odvojene interne blokove predmemorije instrukcija i podataka od 16 KB i 512 KB zajedničke L2 predmemorije koja ne blokira.

Povećanje performansi IA-32 postignuto je ne samo optimizacijom cjevovoda instrukcija i dodavanjem izvršnih jedinica, već i, primjerice, uvođenjem predmemorije u procesorsku jezgru. Obitelj IA-32 predstavila je L1 predmemoriju od 8 KB na čipu po prvi put u Intel-486 procesorima. U Pentium procesorima veličina predmemorije je udvostručena. Prvi predstavnici P6 (Pentium Pro) sadržavali su i L2 cache od 256 ili 512 KB. Međutim, takvo se rješenje u to vrijeme pokazalo preskupim i neisplativim, pa je tehnologija uvedena u Pentium II Dual Independent Bus (DIB) – dvostruki neovisni autobus. Za pristup predmemoriji i za pristup vanjska memorija korištene su zasebne gume. Isto arhitektonsko rješenje korišteno je u prvim modelima Pentium III. Počevši od 1999. (Pentium III Coppermine), L2 predmemorija ponovno je vraćena unutar procesorskih matrica.

Razvoj ideje o SIMD-u za stvarne brojeve bila je tehnologija SSE (Streamed SIMD Extensions), prvi put predstavljen u procesorima Pentium III. SSE blok nadopunjuje MMX tehnologiju s osam 128-bitnih registara XMM0-XMM7 i 32-bitnim kontrolnim i statusnim registrom MXCSR.

Slika 4.9 - Evolucija obrade podataka u procesorima Intel Pentium

4.6.4. Pentium 4 (P7) – mikroarhitektura Net Burst

Procesor Pentium 4 32-bitni je predstavnik obitelji IA-32, po mikroarhitekturi pripada novoj, sedmoj (prema Intel klasifikaciji) generaciji. Softverski gledano, radi se o IA-32 procesoru s još jednim proširenjem sustava instrukcija - SSE2. Što se tiče skupa softverski dostupnih registara, Pentium 4 ponavlja Pentium III procesor. S vanjske, hardverske strane, radi se o procesoru s novom vrstom sistemske sabirnice, u kojoj su uz povećanje frekvencije takta primijenjeni već poznati principi dvostruke (2x) i četverostruke (4x) sinkronizacije, te se poduzima niz mjera kako bi se osigurao rad na dosad nezamislivim frekvencijama. Mikroarhitektura procesora, nazvana Net Burst, dizajnirana je uzimajući u obzir visoke frekvencije i jezgre (više od 1,4 GHz) i sistemske sabirnice (400 MHz).

Slika 4.10 – NetBurst mikroarhitektura

Procesor Pentium 4 je jednočipni. Osim same računalne jezgre, sadrži dvije razine predmemorije. Sekundarna predmemorija, uobičajena za upute i podatke, veličine je 256 KB i ima širinu sabirnice od 256 bita (32 bajta), kao u najnoviji procesori Pentium III. Sekundarna sabirnica predmemorije radi na frekvenciji jezgre, što joj osigurava propusnost od 32x1,4 = 44,8 GB/s na 1,4 GHz. Sekundarna predmemorija ima ECC kontrolu za otkrivanje i ispravljanje pogrešaka. Primarna predmemorija podataka ima istu visoku propusnost (44,8 GB/s), ali je njena veličina prepolovljena (8 KB naspram 16 u Pentiumu III). Nema primarne predmemorije instrukcija u uobičajenom smislu; zamijenjena je predmemorijom praćenja. Pohranjuje nizove mikrooperacija u koje se dekodiraju upute. Ovdje može stati do 12K mikroinstrukcija.

Sučelje sabirnice procesorskog sustava dizajnirano je samo za jednoprocesorske konfiguracije. Sučelje umnogome podsjeća na P6 sabirnicu, a protokol je također fokusiran na istovremeno izvršavanje više transakcija. Poduzete su brojne mjere kako bi se osigurala visoka propusnost. Procesor Pentium 4 ima frekvenciju sabirnice od 400 MHz s "quad pumped" - frekvencija takta sistemske sabirnice je 100 MHz, ali je frekvencija adrese i prijenosa podataka veća. Nove informacije mogu se prenositi linijama sa zajedničkom sinkronizacijom na svakom taktu s frekvencijom od 100 MHz. Za prijenos 2 i 4 puta koristi se sinkronizacija iz izvora podataka.

MP aktuatori (ALU) rade na dvostrukoj frekvenciji, što omogućuje izvršavanje većine cjelobrojnih instrukcija u pola takta. U usporedbi s prethodnim generacijama IA-32, Pentium 4 sadrži najduži instrukcijski cjevovod, koji se sastoji od 20 stupnjeva i tzv. hiperpipelin. U vezi s ovom značajkom, mnogi stručnjaci napominju da će mikroarhitektura NetBurst imati maksimalne performanse izvršavanje predvidljivih (linearnih i cikličkih) dijelova programa, karakterističnih za aplikacije za koje je namijenjen Pentium 4. Na nepredvidivo razgranatim programima, koji uključuju, na primjer, uredske aplikacije, dugačak hipercjevovod pokazuje se manje učinkovitim od P6 cjevovod, ako bi se mogao overclockati na frekvencije od 1,4 GHz i više. Kako bi se djelomično nadoknadio ovaj nedostatak, mehanizmi spekulativnog izvršenja i predviđanja grana značajno su optimizirani.

Materijal u 4. poglavlju temelji se na sintezi radova.

Odricanje

Vjerojatno najtočniji razlog za pojavu ovog materijala može se formulirati na sljedeći način: "nije toliko nužno da postoji, nego je čudno što još nije postojao." I doista: u komentarima na rezultate testa stalno operiramo s pojmovima kao što su "kapacitet predmemorije", "brzina sabirnice procesora", "podrška za proširene skupove instrukcija", ali na web mjestu nema niti jednog članka koji bi sadržavao objašnjenja svih ovih pojmova . Taj je propust, naravno, trebalo otkloniti. Ovaj članak, s podnaslovom “FAQ o x86 CPU-u,” pokušaj je učiniti upravo to. Naravno, neki od njegovih odjeljaka mogu se pripisati ne samo x86 procesorima, a ne samo njihovim stolnim (namijenjenim za instalaciju u PC) verzijama, ali mi svakako ne ciljamo na takav globalizam. Stoga, imajte na umu da za potrebe ovog materijala, osim ako je drugačije izričito navedeno, riječ "procesor" znači "x86 procesor dizajniran za ugradnju u stolna računala." Možda će se u članku u procesu daljnjeg usavršavanja i proširenja pojaviti odjeljci posvećeni poslužiteljskim procesorima ili čak procesorima drugih arhitektura, ali to je stvar budućnosti...

Uvod

Kod i podaci: osnovni princip procesora

Dakle, ako ne pokušavamo ovdje predstaviti “kratki” tečaj informatike za srednju školu, onda jedino što bih želio podsjetiti je da procesor (uz rijetke iznimke) ne izvršava programe napisane u nekom programiranju jezik (od kojih jedan, vi, možda i znate), već neka vrsta "strojnog koda". Odnosno, naredbe za njega su nizovi bajtova koji se nalaze u memoriji računala. Ponekad naredba može biti jednaka jednom bajtu, ponekad je potrebno nekoliko bajtova. Tu se u glavnoj memoriji (RAM, RAM) nalaze i podaci. Mogu biti u zasebnom području ili mogu biti "pomiješani" s kodom. Razlika između koda i podataka je u tome što su podaci ono što iznad čega Procesor izvodi neke operacije. A kod su naredbe koje mu govore, kakva operacija? on mora proizvoditi. Da pojednostavimo, možemo zamisliti program i njegove podatke kao niz bajtova određene konačne duljine, smještenih kontinuirano (da ne kompliciramo) u zajedničkom memorijskom nizu. Na primjer, imamo memorijski niz dug 1.000.000 bajtova, a naš program (zajedno s podacima) sastoji se od bajtova numeriranih od 1.000 do 20.000. Ostali bajtovi su drugi programi ili njihovi podaci, ili jednostavno slobodna memorija koja nije zauzeta ničim korisnim.

Dakle, "strojni kod" su instrukcije procesora smještene u memoriji. Tu se nalaze i podaci. Da bi izvršio instrukciju, procesor je mora pročitati iz memorije. Da bi izvršio operaciju nad podacima, procesor ih mora pročitati iz memorije, te eventualno, nakon što izvrši određenu radnju nad njima, zapisati natrag u memoriju u ažuriranom (promijenjenom) obliku. Naredbe i podaci identificiraju se svojom adresom, koja je u biti serijski broj memorijske lokacije.

Opća načela interakcije

procesor i RAM

Nekoga bi moglo iznenaditi da je prilično velik odjeljak u FAQ-u posvećen x86 CPU-u posvećen objašnjavanju značajki funkcioniranja memorije u moderni sustavi ah, na temelju ove vrste procesora. Međutim, činjenice su tvrdoglava stvar: sami x86 procesori sada sadrže toliko blokova odgovornih posebno za optimizaciju njihovog rada s RAM-om da bi bilo potpuno smiješno ignorirati ovu blisku vezu. Može se čak reći i ovo: budući da su rješenja koja se odnose na optimizaciju rada s memorijom postala sastavni dio samih procesora, onda se sama memorija može smatrati svojevrsnim "privjeskom", čije funkcioniranje izravno utječe na brzinu CPU-a. Bez razumijevanja osobitosti interakcije između procesora i memorije, nemoguće je razumjeti zašto određeni procesor (ovaj ili onaj sustav) izvršava programe sporije ili brže.

Kontroler memorije

Dakle, ranije smo već govorili o činjenici da i naredbe i podaci ulaze u procesor iz RAM memorija. Zapravo, sve je malo kompliciranije. U većini modernih x86 sustava (odnosno računala temeljenih na x86 procesorima) procesor kao uređaj uopće ne može pristupiti memoriji, budući da nema odgovarajuće čvorove. Stoga se pretvara u "srednji" specijalizirani uređaj koji se zove memorijski kontroler, koji se pak pretvara u RAM čipove koji se nalaze na memorijskim modulima. Vjerojatno ste vidjeli module - to su dugačke, uske tekstolitne "daske" (zapravo male ploče) s nizom mikro krugova na njima, umetnute u posebne konektore na matičnoj ploči. Uloga RAM kontrolera je stoga jednostavna: on služi kao svojevrsni "most"* između memorije i uređaja koji je koriste (usput, to ne uključuje samo procesor, ali o tome malo kasnije). U pravilu je memorijski kontroler dio čipseta - skupa čipova koji je osnova matične ploče. Brzina razmjene podataka između procesora i memorije uvelike ovisi o brzini kontrolera; to je jedna od najvažnijih komponenti koja utječe na ukupne performanse računala.

* - usput, memorijski kontroler fizički se nalazi u čipu čipseta, koji se tradicionalno naziva "sjeverni most".

Sabirnica procesora

Svaki procesor nužno je opremljen procesorskom sabirnicom, koja se u x86 CPU okruženju obično naziva FSB (Front Side Bus). Ova sabirnica služi kao komunikacijski kanal između procesora i svih ostalih uređaja u računalu: memorije, video kartice, tvrdi disk, i tako dalje. Međutim, kao što već znamo iz prethodnog odjeljka, između same memorije i procesora nalazi se memorijski kontroler. Sukladno tome: procesor komunicira preko FSB-a s memorijskim kontrolerom, koji, pak, komunicira putem posebne sabirnice (nazovimo je, bez daljnjega, "memorijska sabirnica") s RAM modulima na ploči. No, ponavljamo: budući da klasični x86 CPU ima samo jednu “vanjsku” sabirnicu, ona služi ne samo za rad s memorijom, već i za komunikaciju između procesora i svih ostalih uređaja.

Razlike između tradicionalnih

x86 CPU arhitektura i K8/AMD64

Revolucionarni pristup AMD-a leži u činjenici da su njegovi procesori s arhitekturom AMD64 (i mikroarhitekturom, koja se konvencionalno naziva "K8") opremljeni mnogim "vanjskim" sabirnicama. U ovom slučaju, jedna ili više HyperTransport sabirnica koristi se za komunikaciju sa svim uređajima osim memorije, a zasebna grupa od jedne ili dvije (u slučaju dvokanalnog kontrolera) sabirnice koristi se isključivo za rad procesora s memorijom. Prednost integriranja memorijskog kontrolera izravno u procesor je očita: "put od jezgre do memorije" postaje osjetno "kraći", što vam omogućuje brži rad s RAM-om. Istina, ovaj pristup ima i nedostataka. Tako, na primjer, ako su prethodno uređaji poput tvrdi disk ili bi video kartice mogle raditi s memorijom putem namjenskog, neovisnog kontrolera - tada su u slučaju arhitekture AMD64 prisiljene raditi s RAM-om preko kontrolera smještenog na procesoru. Budući da je CPU u ovoj arhitekturi jedini uređaj s izravnim pristupom memoriji. De facto, u sukobu “vanjski kontrolor vs. integrirani”, pojavio se paritet: s jedne strane, AMD je trenutno jedini proizvođač stolnih x86 procesora s integriranim memorijskim kontrolerom, s druge strane, čini se da je tvrtka prilično zadovoljna ovim rješenjem i neće ga napustiti . Treće, Intel također neće odustati od vanjskog kontrolera i prilično je zadovoljan "klasičnom shemom", dokazanom tijekom godina.

radna memorija

Širina memorijske sabirnice, N-kanalni memorijski kontroleri

Od danas, sva memorija koja se koristi u modernim x86 stolnim sustavima ima 64-bitnu sabirnicu. To znači da se u jednom ciklusu takta količina informacija koja je višekratnik od 8 bajtova može simultano prenijeti ovom sabirnicom (8 bajtova za SDR sabirnice, 16 bajtova za DDR sabirnice). Jedina stvar koja se ističe je memorija tipa RDRAM, koja se koristila u sustavima temeljenim na Intel Pentium 4 procesorima u zoru NetBurst arhitekture, ali sada je ovaj smjer prepoznat kao slijepa ulica za x86 računala (usput, ista tvrtka Intel imala je ruku u tome, koja je svojedobno aktivno promovirala ovaj tip memorija). Nešto zabune izazivaju samo dvokanalni kontroleri, koji omogućuju istovremeni rad s dvije odvojene 64-bitne sabirnice, zbog čega neki proizvođači tvrde da imaju određenu “128-bitnu” sposobnost. Ovo je, naravno, čista profanacija. Aritmetika na razini 1. razreda, nažalost, u ovom slučaju ne funkcionira: 2x64 uopće nije jednako 128. Zašto? Da, samo zato što čak ni najmoderniji x86 CPU-i (pogledajte odjeljak FAQ “64-bitna proširenja klasične x86 (IA32) arhitekture” u nastavku) ne mogu raditi sa 128-bitnom sabirnicom i 128-bitnim adresiranjem. Grubo govoreći: dvije neovisne paralelne ceste, svaka široka 2 metra, mogu omogućiti istovremeni prolaz dva automobila, široka 2 metra - ali nikako jednog, širokog 4 metra. Na isti način, N-kanalni memorijski kontroler može povećati brzinu rada s podacima N puta (i onda više teoretski nego praktično) - ali ni na koji način ne može povećati bitni kapacitet tih podataka. Širina memorijske sabirnice u svim modernim kontrolerima koji se koriste u x86 sustavima je 64 bita - neovisno o tome nalazi li se taj kontroler u čipsetu ili u samom procesoru. Neki kontroleri opremljeni su s dva neovisna 64-bitna kanala, ali to ni na koji način ne utječe na širinu memorijske sabirnice - samo na brzinu čitanja i pisanja informacija.

Brzina čitanja i pisanja

Brzina čitanja i zapisivanja informacija u memoriju teoretski je ograničena isključivo propusnošću same memorije. Na primjer, dvokanalni DDR400 memorijski kontroler teoretski može osigurati brzine čitanja i pisanja informacija jednake 8 bajtova (širina sabirnice) * 2 (broj kanala) * 2 (DDR protokol, koji osigurava prijenos 2 paketa podataka po ciklus takta) * 200"000"000 (stvarna radna frekvencija memorijske sabirnice je 200 MHz, odnosno 200"000"000 ciklusa takta u sekundi). Vrijednosti dobivene kao rezultat praktičnih testova u pravilu su nešto niže od teoretskih: to je zbog "nesavršenog" dizajna memorijskog kontrolera, plus režijskih troškova (kašnjenja) uzrokovanih radom predmemoriranja podsustava samog procesora (pogledajte odjeljak o predmemorij procesora u nastavku). No, glavna “kvaka” nije čak ni u prekrivačima povezanim s radom kontrolera i podsustava za predmemoriju, već u činjenici da brzina “linearnog” čitanja ili pisanja nije jedina karakteristika koja utječe na stvarnu brzinu procesor s RAM-om. Da bismo razumjeli koje komponente čine stvarnu brzinu procesora i memorije, moramo, uz linearnu brzinu čitanja ili pisanja, također uzeti u obzir takvu karakteristiku kao što je latencija.

Latencija

Latencija nije manja važna karakteristika sa stajališta brzine memorijskog podsustava, nego brzine “pumpanja podataka”, ali potpuno drugačije, u biti. Velika brzina razmjene podataka je dobra kada je njihova veličina relativno velika, ali ako trebamo “malo po malo s raznih adresa”, onda latencija dolazi do izražaja. Što je? Općenito, vrijeme potrebno za početak čitanja informacija s određene adrese. I doista: od trenutka kada procesor pošalje naredbu za čitanje (pisanje) memorijskom kontroleru do trenutka kada se ta operacija izvrši, prođe određeno vrijeme. Štoviše, to uopće nije jednako vremenu potrebnom za prijenos podataka. Primivši naredbu za čitanje ili pisanje od procesora, memorijski kontroler mu "indicira" s kojom adresom želi raditi. Pristup bilo kojoj nasumično odabranoj adresi ne može se ostvariti trenutno; to zahtijeva određeno vrijeme. Dolazi do kašnjenja: adresa je navedena, ali memorija još nije spremna za pristup njoj. Općenito, to se kašnjenje naziva latencija. U različiti tipovi pamćenje je drugačije. Na primjer, DDR2 memorija ima u prosjeku mnogo veće latencije od DDR (pri istoj frekvenciji prijenosa podataka). Kao rezultat toga, ako su podaci u programu smješteni "kaotično" i u "malim komadićima", brzina njihovog čitanja postaje mnogo manje važna od brzine pristupa "početku dijela", jer kašnjenja pri prelasku na sljedeća adresa utječe na performanse sustava mnogo više od brzine čitanja ili pisanja.

"Natjecanje" između brzine čitanja (pisanja) i latencije jedna je od glavnih glavobolja za programere modernih sustava: nažalost, povećanje brzine čitanja (pisanja) gotovo uvijek dovodi do povećanja latencije. Na primjer, memorija tipa SDR (PC66, PC100, PC133) ima u prosjeku bolju (nižu) latenciju od DDR-a. Zauzvrat, DDR2 ima još veću latenciju (tj. goru) od DDR-a.

Treba imati na umu da "ukupna" latencija memorijskog podsustava ne ovisi samo o njemu samom, već i o memorijskom kontroleru i njegovoj lokaciji - svi ti čimbenici također utječu na latenciju. Zato je AMD, u procesu razvoja AMD64 arhitekture, odlučio problem velike latencije riješiti “jednim potezom” integracijom kontrolera izravno u procesor - kako bi se “skratio razmak” između procesorske jezgre i procesora. RAM modula što je više moguće. Ideja je bila uspješna, ali uz visoku cijenu: sada sustav temeljen na specifičnoj procesorskoj jedinici AMD64 arhitekture može raditi samo s memorijom za koju je dizajniran njegov kontroler. Vjerojatno je to razlog zašto se Intel još nije odlučio na tako drastičan korak, već radije djeluje tradicionalnim metodama: poboljšanjem memorijskog kontrolera u čipsetu i Prefetch mehanizma u procesoru (vidi dolje za detalje).

Zaključno, napominjemo da se pojmovi "brzina čitanja / pisanja" i "latencija" općenito primjenjuju na bilo koju vrstu memorije - uključujući ne samo klasični DRAM (SDR, Rambus, DDR, DDR2), već i predmemoriju (vidi ispod).

Procesor: Opće informacije

Koncept arhitekture

Arhitektura kao kompatibilnost koda

Sigurno ste često nailazili na pojam “x86”, ili “Intel-kompatibilan procesor” (ili “IBM PC kompatibilan” - ali to je u vezi s računalom). Ponekad se koristi i izraz "kompatibilan s Pentiumom" (zašto Pentium - shvatit ćete malo kasnije). Što se zapravo krije iza svih ovih imena? U ovom trenutku, sljedeća jednostavna formulacija izgleda najispravnija sa stanovišta autora: moderni x86 procesor je procesor sposoban ispravno izvršavati strojni kod IA32 arhitekture (arhitektura 32-bitnih Intel procesora). U prvoj aproksimaciji, ovo je kod koji izvršava procesor i80386 (popularno poznat kao "386"), ali glavni skup IA32 instrukcija konačno je formiran s izdavanjem procesora Intel Pentium Pro. Što znači "osnovni skup" i koji drugi postoje? Najprije odgovorimo na prvi dio pitanja. "Osnovno" u ovom slučaju znači da se korištenjem isključivo ovog skupa instrukcija može napisati bilo koji program koji se općenito može napisati za x86 procesor (ili IA32, ako vam je draže).

Osim toga, IA32 arhitektura ima "službena" proširenja (dodatne skupove instrukcija) od developera same arhitekture, Intela: MMX, SSE, SSE2 i SSE3. Postoje i "neslužbeni" (ne-Intel) prošireni skupovi naredbi: EMMX, 3DNow! i Prošireni 3DNow! - razvio ih je AMD. Međutim, "službeno" i "neslužbeno" u ovom slučaju su relativni koncept - de facto, sve se svodi na činjenicu da su neke ekstenzije skupa instrukcija priznate od strane Intela, kao developera originalnog skupa, a neke su ne, dok programeri koriste ono što je najbolje za njih sve odgovara. Postoji jedno jednostavno pravilo dobrog bontona kada su u pitanju prošireni skupovi instrukcija: prije njihove uporabe program treba provjeriti podržava li ih procesor. Ponekad dolazi do odstupanja od ovog pravila (i može dovesti do neispravnog rada programa), ali objektivno to je problem neispravno napisanog softvera, a ne procesora.

Čemu služe dodatni skupovi naredbi? Prije svega, za povećanje performansi pri izvođenju određenih operacija. Jedna naredba iz sekundarnog skupa obično izvodi radnju koja bi zahtijevala mali program koji se sastoji od naredbi iz glavnog skupa. Opet, u pravilu, procesor izvršava jednu instrukciju brže od niza koji zamjenjuje. Međutim u 99% slučajeva ništa što se nije moglo učiniti pomoću osnovnih naredbi ne može se učiniti pomoću naredbi iz dodatnog skupa.

Dakle, gore spomenuta provjera programa za podršku dodatnih skupova instrukcija od strane procesora trebala bi obavljati vrlo jednostavnu funkciju: ako, na primjer, procesor podržava SSE, tada ćemo brojati brzo i koristeći instrukcije iz SSE skupa. Ako ne, brojat ćemo sporije, koristeći naredbe iz glavnog skupa. Ispravno napisan program mora tako djelovati. Međutim, sada gotovo nitko ne provjerava podršku procesora za MMX, budući da svi CPU-i izdani u posljednjih 5 godina zajamčeno podržavaju ovaj skup. Za referencu, ovdje je tablica koja sažima informacije o podršci raznih proširenih skupova naredbi od strane različitih stolnih (dizajniranih za stolna računala) procesora.

| CPU | |||||||

| Intel Pentium II | |||||||

| Intel Celeron do 533 MHz | |||||||

| Intel Pentium III | |||||||

| Intel Celeron 533-1400 MHz | |||||||

| Intel Pentium 4 | |||||||

| Intel Celeron od 1700 MHz | |||||||

| Intel Celeron D | |||||||

| Intel Pentium 4 eXtreme Edition | |||||||

| Intel Pentium eXtreme Edition | |||||||

| Intel Pentium D | |||||||

| AMD K6 | |||||||

| AMD K6-2 | |||||||

| AMD K6-III | |||||||

| AMD Athlon | |||||||

| AMD Duron do 900 MHz | |||||||

| AMD Athlon XP | |||||||

| AMD Duron od 1000 MHz | |||||||

| AMD Athlon 64 / Athlon FX | |||||||

| AMD Sempron | |||||||

| AMD Athlon 64 X2 | |||||||

| PREKO C3 |

*ovisno o modifikaciji

U ovom trenutku, sve popularne desktop softver(Windows i Linux operativni sustavi, uredski paketi, računalne igrice, itd.) razvija se posebno za x86 procesore. Radi (s izuzetkom programa koji se "loše ponašaju") na bilo kojem x86 procesoru, bez obzira na to tko ga je napravio. Stoga su umjesto izraza “Intel-kompatibilan” ili “Pentium-kompatibilan” usmjerenih na developera originalne arhitekture, počeli koristiti neutralni naziv: “x86-kompatibilan procesor”, “procesor s x86 arhitekturom”. U ovom slučaju, "arhitektura" znači kompatibilnost s određenim skupom instrukcija, odnosno, može se reći, "arhitektura procesora s programerskog gledišta". Postoji još jedno tumačenje istog pojma.

Arhitektura kao karakteristika obitelji procesora

"Zhelezyachniki" - ljudi koji uglavnom ne rade sa softverom, već s hardverom, shvaćaju "arhitekturu" na malo drugačiji način (iako je ispravnije da se ono što oni zovu "arhitektura" zove "mikroarhitektura", ali de facto prefiks " mikro" često se izostavlja). Za njih je "CPU arhitektura" određeni skup svojstava svojstven cijeloj obitelji procesora, koji se obično proizvode godinama (drugim riječima, "unutarnji dizajn", "organizacija" ovih procesora). Tako će vam, na primjer, svaki stručnjak za x86 CPU reći da je procesor s ALU-ovima koji rade na dvostrukoj frekvenciji, QDR sabirnicom, Trace cacheom i mogućom podrškom za tehnologiju Hyper-Threading "procesor arhitekture NetBurst" (ne budite uznemiren nepoznatim pojmovima - svi će biti objašnjeni malo kasnije). A Intel Pentium Pro, Pentium II i Pentium III procesori su “P6 arhitektura”. Stoga je koncept "arhitekture" u odnosu na procesore pomalo dvosmislen: može se shvatiti i kao kompatibilnost s određenim pojedinačnim skupom instrukcija i kao skup hardverskih rješenja svojstvenih određenoj prilično širokoj skupini procesora. Naravno, takav dualizam jednog od temeljnih pojmova nije baš zgodan, ali to je tako i teško da će se nešto promijeniti u skoroj budućnosti...

64-bitna proširenja klasične x86 (IA32) arhitekture

Nedavno su oba vodeća proizvođača x86 CPU-a najavila dvije gotovo identične* tehnologije (međutim, AMD to radije naziva arhitekturom), zahvaljujući kojima su klasični x86 (IA32) CPU-i dobili 64-bitni status. U slučaju AMD-a ovu tehnologiju dobio naziv "AMD64" (64-bitni AMD arhitektura), u slučaju Intela - “EM64T” (poboljšana 64-bitna memorijska tehnologija). Također, ugledni starci koji su upoznati s poviješću problema ponekad koriste naziv “x86-64” - kao opću oznaku za sva 64-bitna proširenja x86 arhitekture, nevezana za registrirane robne marke bilo kojeg proizvođača. De facto, korištenje jednog od tri gore navedena naziva više ovisi o osobnim preferencijama korisnika nego o stvarnim razlikama - jer razlike između AMD64 i EM64T stanu na vrh vrlo tanke igle. Osim toga, sam AMD je uveo "brand" naziv "AMD64" tek nedugo prije najave vlastitih procesora temeljenih na ovoj arhitekturi, a prije toga je sasvim mirno koristio neutralniji "x86-64" u svojim dokumentima. Međutim, na ovaj ili onaj način, sve se svodi na jednu stvar: neki interni registri procesora postali su 64-bitni umjesto 32-bitni, 32-bitne x86 kodne instrukcije dobile su svoje 64-bitne analoge, osim toga, količina adresabilna memorija (uključujući ne samo fizičku, već i virtualnu) višestruko se povećala (zbog činjenice da je adresa dobila 64-bitni format umjesto 32-bitnog). Broj marketinških špekulacija na temu “64-bita” premašio je sve razumne granice, stoga bismo trebali posebno pažljivo razmotriti prednosti ove inovacije. Dakle: što se zapravo promijenilo, a što nije?

* - Argumenti da je Intel "drsko kopirao EM64T iz AMD64" ne izdržavaju kritiku. I to uopće ne zato što nije tako - nego zato što uopće nije "bezobrazno". Postoji takav koncept: "ugovor o unakrsnom licenciranju". Ako do takvog dogovora dođe, to znači da svi razvoji jedne tvrtke na određenom području automatski postaju dostupni drugoj, kao što i razvoji druge automatski postaju dostupni prvoj. Intel je iskoristio unakrsno licenciranje za razvoj EM64T, koristeći AMD64 kao osnovu (što nitko nikada nije zanijekao). AMD je iskoristio isti ugovor za uvođenje podrške za SSE2 i SSE3 dodatne skupove instrukcija koje je razvio Intel u svoje procesore. I u tome nema ničeg sramotnog: budući da smo pristali "dijeliti" razvoj događaja, znači da moramo dijeliti.

Što se nije promijenilo? Prije svega, brzina procesora. Bila bi očigledna glupost pretpostaviti da će isti procesor, kada se prebaci s uobičajenog 32-bitnog na 64-bitni način (a svi trenutni x86 CPU-i nužno podržavaju 32-bitni način), raditi 2 puta brže. Naravno, u nekim slučajevima može doći do nekog ubrzanja korištenjem 64-bitne aritmetike cijelih brojeva - ali broj tih slučajeva je vrlo ograničen i ne utječu na većinu modernog korisničkog softvera. Usput: zašto smo upotrijebili izraz "64-bitna aritmetika cijelog broja"? Ali zato što blokovi operacija s pomičnim zarezom (vidi dolje) u svim x86 procesorima odavno više nisu 32-bitni. Pa čak ni 64-bitni. Klasični x87 FPU (vidi dolje), koji je konačno postao dio CPU-a još u danima dobrog starog 32-bitnog Intel Pentiuma - već je bio 80-bitni. Operandi SSE i SSE2/3 instrukcija su 128-bitni! U tom smislu, arhitektura x86 prilično je paradoksalna: unatoč činjenici da su procesori ove arhitekture formalno ostali 32-bitni dosta dugo vremena - bitni kapacitet onih blokova gdje je “b O“veći bitni kapacitet” je doista bio potreban - povećavan je potpuno neovisno o ostalima. Na primjer, procesori AMD Athlon XP i Intel Pentium 4 “Northwood” kombinirali su jedinice koje su radile s 32-bitnim, 80-bitnim i 128-bitnim operandima. Samo su glavni skup instrukcija (naslijeđen od prvog procesora IA32 arhitekture - Intel 386) i adresiranje memorije (maksimalno 4 gigabajta, ne računajući "perverzije" poput Intel PAE) ostali 32-bitni.

Dakle, činjenica da su AMD i Intel procesori postali “formalno 64-bitni”, u praksi nam je donijela samo tri poboljšanja: pojavu naredbi za rad sa 64-bitnim cijelim brojevima, povećanje broja i/ili bitne dubine registara, i povećanje memorije maksimalnog adresabilnog volumena. Napomena: nitko ne poriče stvarne prednosti ovih inovacija (osobito treće!). Baš kao što nitko ne poriče zasluge AMD-a u promicanju ideje o “modernizaciji” (zbog uvođenja 64-bitnih) x86 procesora. Samo želimo upozoriti na pretjerana očekivanja: ne biste se trebali nadati da će računalo kupljeno "u cjenovnoj klasi VAZ-a" postati "vrlovit Mercedes" bez instaliranja 64-bitnog softvera. Nema čuda na svijetu...

Jezgra procesora

Razlike između jezgri iste mikroarhitekture

"Procesorska jezgra" (obično se jednostavno naziva "jezgra" radi sažetosti) je specifično utjelovljenje [mikro]arhitekture (tj. "arhitekture u hardverskom smislu riječi") koja je standard za cijelu seriju procesora. Na primjer, NetBurst je mikroarhitektura na kojoj se nalaze mnogi današnji Intelovi procesori: Celeron, Pentium 4, Xeon. Mikroarhitektura postavlja opća načela: dugi cjevovod, korištenje određene vrste predmemorije koda prve razine (Trace cache) i druge "globalne" značajke. Jezgra je specifičnije utjelovljenje. Na primjer, procesori mikroarhitekture NetBurst sa sabirnicom od 400 MHz, predmemorijom druge razine od 256 kilobajta i bez Podrška za Hyper-Threading je više-manje potpuni opis jezgre Willamette. Ali jezgra Northwood ima predmemoriju druge razine od 512 kilobajta, iako se također temelji na NetBurstu. Jezgra AMD Thunderbird temelji se na mikroarhitekturi K7, ali ne podržava SSE skup instrukcija, ali jezgra Palomino podržava.

Dakle, možemo reći da je "jezgra" specifično utjelovljenje određene mikroarhitekture "u siliciju", koja ima (za razliku od same mikroarhitekture) određeni skup strogo definiranih karakteristika. Mikroarhitektura je amorfna; ona opisuje opće principe dizajna procesora. Jezgra je, konkretno, mikroarhitektura, “obrasla” svakakvim parametrima i karakteristikama. Vrlo je rijetko da procesori mijenjaju mikroarhitekturu zadržavajući isto ime. I, obrnuto, gotovo svaki naziv procesora je "promijenio" svoju jezgru barem nekoliko puta tijekom svog postojanja. Na primjer, opći naziv serije AMD procesora je "Athlon XP" - ovo je jedna mikroarhitektura (K7), ali čak četiri jezgre (Palomino, Thoroughbred, Barton, Thorton). Različite jezgre izgrađene na istoj mikroarhitekturi mogu imati, između ostalog, različite razine performansi.

revizije

Revizija je jedna od izmjena jezgre koja se vrlo malo razlikuje od prethodne, zbog čega ne zaslužuje naziv “nova jezgra”. U pravilu, proizvođači procesora ne prave veliku stvar oko izdavanja sljedeće revizije; to se događa "u radnom stanju". Dakle, čak i ako kupite isti procesor, potpuno sličnog imena i karakteristika, ali s razmakom od oko šest mjeseci, vrlo je moguće da će zapravo biti malo drugačiji. Izdavanje nove revizije obično je povezano s nekim manjim poboljšanjima. Na primjer, uspjeli smo malo smanjiti potrošnju energije, ili smanjiti napon napajanja, ili optimizirati nešto drugo, ili je otklonjeno nekoliko manjih grešaka. Sa stajališta performansi, ne sjećamo se niti jednog primjera gdje se jedna revizija kernela toliko značajno razlikovala od druge da o tome ima smisla govoriti. Iako je ova opcija čisto teoretski moguća - na primjer, optimiziran je jedan od procesorskih blokova odgovornih za izvršavanje nekoliko naredbi. Ukratko, možemo reći da se najčešće ne isplati zamarati revizijama procesora: u vrlo rijetkim slučajevima promjena revizije čini neke temeljne promjene na procesoru. Dovoljno je samo znati da tako nešto postoji - isključivo za opći razvoj.

Frekvencija jezgre

U pravilu se ovaj parametar kolokvijalno naziva "frekvencija procesora". Iako je u općem slučaju definicija "radne frekvencije jezgre" ipak ispravnija, budući da uopće nije nužno da sve komponente CPU-a rade na istoj frekvenciji kao jezgra (najčešći primjer suprotnog je bio stari “slot” x86 CPU-i - Intel Pentium II i Pentium III za Slot 1, AMD Athlon za Slot A - njihova L2 predmemorija funkcionirala je na 1/2, a ponekad čak i na 1/3 frekvencije jezgre). Druga uobičajena zabluda je uvjerenje da frekvencija jezgre jedinstveno određuje performanse. Zapravo, ovo je dvostruko pogrešno: prvo, svaka specifična procesorska jezgra (ovisno o tome kako je dizajnirana, koliko izvršnih jedinica sadrži različite vrste itd. itd.) mogu izvršiti različiti broj naredbi u jednom ciklusu takta, ali je frekvencija samo broj takvih ciklusa takta u sekundi. Prema tome (usporedba u nastavku je, naravno, vrlo pojednostavljena i stoga vrlo proizvoljna), procesor čija jezgra izvršava 3 instrukcije po taktu može imati trećinu nižu frekvenciju od procesora koji izvršava 2 instrukcije po taktu - i u isto vrijeme imati potpuno sličnu izvedbu.

Drugo, čak i unutar iste jezgre, povećanje frekvencije ne dovodi uvijek do proporcionalnog povećanja performansi. Ovdje će vam znanje koje ste mogli prikupiti iz odjeljka "Opća načela interakcije između procesora i RAM-a" biti vrlo korisno. Činjenica je da brzina izvršavanja naredbi procesorske jezgre nije jedini pokazatelj koji utječe na brzinu izvršavanja programa. Jednako je važna brzina kojom naredbe i podaci stižu do CPU-a. Zamislimo, čisto teoretski, takav sustav: brzina procesora je 10 000 naredbi u sekundi, brzina memorije je 1000 bajtova u sekundi. Pitanje: čak i ako pretpostavimo da jedna naredba ne zauzima više od jednog bajta, a nemamo podataka uopće, kojom brzinom će se program izvršavati u takvom sustavu? Točno: ne više od 1000 naredbi u sekundi, a CPU performanse nemaju apsolutno nikakve veze s tim: nećemo biti ograničeni njome, već brzinom na koje naredbe ulaze u procesor. Dakle, trebali biste razumjeti: nemoguće je kontinuirano povećavati samo jednu frekvenciju jezgre, bez istovremenog ubrzavanja memorijskog podsustava, jer u ovom slučaju, počevši od određene faze, povećanje frekvencije procesora više neće utjecati na povećanje performansi sustava u cjelini.

Značajke formiranja imena procesora

Prije, dok je nebo bilo plavije, pivo je bilo bolje, a djevojke ljepše, prerađivači su se zvali jednostavno: ime proizvođača + naziv asortiman modela+ učestalost. Na primjer: "AMD K6-2 450 MHz". Trenutno su se oba velika proizvođača odmaknula od te tradicije i umjesto učestalosti koriste neke nerazumljive brojke koje označavaju tko zna što. Sljedeća dva odjeljka posvećena su kratkom objašnjenju što ti brojevi zapravo znače.

Ocjene iz AMD-a

Poznat je razlog zašto je AMD iz naziva svojih procesora “izbacio” frekvenciju i zamijenio je nekim apstraktnim brojem: nakon pojave procesora Intel Pentium 4, koji radi na vrlo visokim frekvencijama, AMD-ovi procesori uz njega su počeli “loše izgledati u izlogu” - kupac nije vjerovao da CPU s frekvencijom od, na primjer, 1500 MHz može prestići CPU s frekvencijom od 2000 MHz. Stoga je frekvencija u nazivu zamijenjena ocjenom. Formalno ("de jure", da tako kažemo) tumačenje ove ocjene od strane AMD-a zvučalo je malo drugačije u različitim vremenima, ali nikada nije zvučalo u obliku u kojem su ga korisnici percipirali: AMD procesor s određenom ocjenom trebao bi biti kao barem ne sporiji od procesora Intel Pentium 4 s frekvencijom koja odgovara ovoj ocjeni. Pritom, nikome nije bila posebna tajna da je upravo takva interpretacija bila krajnji cilj uvođenja rejtinga. Općenito, svi su sve savršeno razumjeli, ali AMD se marljivo pretvarao da nema nikakve veze s tim :). Ne treba joj zamjeriti na tome: u natjecanju vrijede sasvim druga pravila nego u viteškim borbama. Štoviše, rezultati neovisnih testova pokazali su: općenito, AMD svojim procesorima dodjeljuje prilično poštene ocjene. Zapravo, sve dok je tako, nema smisla buniti se protiv korištenja ocjene. Istina, jedno pitanje ostaje otvoreno: za što (zanima nas, naravno, de facto stanje, a ne objašnjenja marketinškog odjela) će se vezati ocjena AMD procesora malo kasnije, kada Intel počne proizvoditi neke drugi procesor umjesto Pentiuma 4?

Intelov broj procesora

Ono što morate odmah zapamtiti: Broj procesora (u daljnjem tekstu PN) za Intel procesore nije ocjena. Ne ocjena izvedbe ili ocjena bilo čega drugog. Zapravo, to je jednostavno "stavka", stavka na popisu inventara čija je jedina svrha osigurati da se linija koja predstavlja jedan procesor razlikuje od linije koja predstavlja drugi. Unutar serije (prva znamenka PN), druge dvije znamenke, u načelu, mogu nešto reći, ali s obzirom na prisutnost tablica koje pokazuju potpunu korespondenciju između PN i stvarnih parametara, ne vidimo puno smisla u memoriranju koji - to su srednje korespondencije. Intelova motivacija za uvođenje PN (umjesto specificiranja CPU frekvencije) je složenija od AMD-ove. Potreba za uvođenjem PN-a (kako to objašnjava sam Intel) prvenstveno je posljedica činjenice da dva glavna konkurenta imaju različite pristupe pitanju jedinstvenosti naziva CPU-a. Na primjer, za AMD naziv "Athlon 64 3200+" može značiti četiri procesora s malo različitim tehničke karakteristike(ali s istom “ocjenom”). Intel je mišljenja da ime procesora mora biti jedinstveno, pa je kompanija ranije morala “izmicati” dodajući različita slova vrijednosti frekvencije u nazivu, što je dovodilo do zabune. U teoriji, PN je trebao eliminirati ovu zabunu. Teško je reći je li cilj postignut: svejedno je raspon Intelovih procesora ostao prilično složen. S druge strane, to je neizbježno, jer je asortiman proizvoda prevelik. No, bez obzira na sve ostalo, jedan de facto učinak je definitivno postignut: sada samo stručnjaci koji se razumiju u problematiku mogu brzo i točno “napamet” po imenu procesora reći kakav je i kakve će njegove performanse biti u usporedbi s drugim procesorima. procesori. Koliko je dobro? Teško je reći. Radije bismo se suzdržali od komentara.

Mjerenje brzine "u megahercima" - kako je to moguće?

To nikako nije moguće jer se brzina ne mjeri u megahercima, kao što se ni udaljenost ne mjeri u kilogramima. No, gospoda trgovci odavno su shvatili da u verbalnom dvoboju između fizičara i psihologa uvijek pobjeđuje potonji – i bez obzira na to tko je zapravo u pravu. Zato čitamo o "ultra-brzom FSB-u od 1066 MHz", bolno pokušavajući shvatiti kako se brzina može mjeriti pomoću frekvencije. Zapravo, budući da je takav izopačeni trend zaživio, samo vam treba biti jasno što to znači. Ono što mislimo je sljedeće: ako "popravimo" širinu sabirnice na N bitova, tada je njegova propusnost zapravo će ovisiti o frekvenciji na kojoj sabirnica radi i koliko podataka može prenijeti po taktu. Na običnoj procesorskoj sabirnici s “jednom” brzinom (takva je sabirnica bila npr. procesor Intel Pentium III) po taktu se prenosi 64 bita, odnosno 8 bajtova. Prema tome, ako je radna frekvencija sabirnice 100 MHz (100"000"000 ciklusa takta u sekundi), tada će brzina prijenosa podataka biti jednaka 8 bajtova * 100"000"000 herca ~= 763 megabajta u sekundi (i ako se broji u "decimalnim megabajtima" , u kojima je uobičajeno uzeti u obzir tokovi podataka, pa još ljepše - 800 megabajta u sekundi). U skladu s tim, ako DDR sabirnica radi na istih 100 megaherca, sposobna prenijeti dvostruku količinu podataka u jednom taktu, brzina će se povećati točno dva puta. Stoga bi se, prema paradoksalnoj logici gospode trgovaca, ovaj autobus trebao zvati "200 MHz". A ako je to i QDR (Quad Data Rate) sabirnica, onda zapravo ispada da ima "400 MHz", budući da prenosi četiri paketa podataka u jednom taktu. Iako je stvarna radna frekvencija sve tri gore opisane sabirnice ista - 100 megaherca. Tako je "megaherc" postao sinonim za brzinu.

Tako se QDR sabirnica (s "četverostrukom" brzinom), koja radi na stvarnoj frekvenciji od 266 megaherca, čudesno pokazuje na "1066 megaherca". Broj "1066" u ovom slučaju predstavlja činjenicu da je njegova propusnost točno 4 puta veća od "jednobrzinske" sabirnice koja radi na istoj frekvenciji. Jeste li već zbunjeni?.. Naviknite se! Ovo nije nekakva teorija relativnosti, ovdje je sve puno kompliciranije i zanemarenije... Ipak, ovdje je najvažnije upamtiti jedno jednostavno načelo: ako radimo takvu perverziju kao što je usporedba brzine dvaju autobusa s jedan drugoga “u megahercima”, tada moraju biti iste širine. Inače, ispada kao na jednom forumu, gdje je osoba ozbiljno tvrdila da je propusnost AGP2X ("133 MHz", ali 32-bitni sabirnica) - veća od propusnosti FSB-a Pentiuma III 800 (stvarna frekvencija 100 MHz, širina 64 bita).

Nekoliko riječi o nekim pikantnim značajkama DDR i QDR protokola

Kao što je gore spomenuto, u DDR načinu rada dvostruka količina informacija prenosi se sabirnicom u jednom ciklusu takta, au QDR načinu rada učetverostručuje se. Istina, u dokumentima usmjerenim više na veličanje postignuća proizvođača nego na objektivno pokrivanje stvarnosti, iz nekog razloga uvijek zaboravljaju navesti jedno malo "ali": Načini dvostruke i četverostruke brzine omogućeni su samo tijekom paketnog prijenosa podataka. Odnosno, ako smo zatražili par megabajta iz memorije s adrese X na adresu Y, onda da, ta dva megabajta će se prenijeti dvostrukom/četverostrukom brzinom. Ali sam zahtjev za podacima šalje se sabirnicom jednom brzinom - Stalno ! Sukladno tome, ako imamo puno zahtjeva, a veličina podataka koji se šalju nije jako velika, tada će količina podataka koja „putuje“ sabirnicom jednom brzinom (a zahtjev je također podatak) biti gotovo jednaka količini koja se prenosi dvostrukom ili četverostrukom brzinom. Čini se da nam nitko nije otvoreno lagao, čini se da DDR i QDR stvarno rade, ali... kako kaže jedan stari vic: “ili je on nekome ukrao bundu, ili je netko njemu ukrao bundu, ali nešto nije u redu s bundom..." ;)

Veliki blok procesor

Predmemorija

Opći opis i princip rada

Svi moderni procesori imaju predmemoriju (na engleskom - cache). Predmemorija je posebna vrsta memorije (glavna značajka koja bitno razlikuje predmemoriju od RAM-a je brzina rada), koja je neka vrsta "međuspremnika" između memorijskog kontrolera i procesora. Ovaj se međuspremnik koristi za povećanje brzine rada s RAM-om. Kako? Sada pokušajmo objasniti. U isto vrijeme, odlučili smo napustiti usporedbe koje imaju miris dječjeg vrtića, a koje se često nalaze u popularnoj literaturi o temama procesora (bazeni povezani cijevima različitih promjera itd., itd.). Uostalom, osoba koja je pročitala članak do ove točke i nije zaspala vjerojatno može izdržati i "probaviti" čisto tehničko objašnjenje, bez bazena, mačaka i maslačka.

Dakle, zamislimo da imamo puno relativno spore memorije (neka to bude RAM veličine 10.000.000 bajtova) i relativno malo vrlo brze memorije (neka to bude predmemorija veličine samo 1024 bajta). Kako možemo iskoristiti ovaj nesretni kilobajt za povećanje brzine rada sa cjelokupnom memorijom općenito? Ali ovdje treba imati na umu da se podaci tijekom rada programa u pravilu ne bacaju nepromišljeno s mjesta na mjesto - to promijeniti. Očitali su vrijednost neke varijable iz memorije, dodali joj neki broj i zapisali je natrag na isto mjesto. Prebrojali smo niz, sortirali ga uzlaznim redoslijedom i ponovno zapisali u memoriju. To jest, u jednom trenutku program ne radi s cijelom memorijom, već, u pravilu, s relativno malim fragmentom. Koje se rješenje nameće samo po sebi? Tako je: učitajte ovaj fragment u "brzu" memoriju, obradite ga tamo, a zatim ga zapišite natrag u "sporu" memoriju (ili ga jednostavno izbrišite iz predmemorije ako se podaci nisu promijenili). Općenito, to je upravo način na koji radi predmemorija procesora: sve informacije pročitane iz memorije završavaju ne samo u procesoru, već iu predmemorije. A ako je ista informacija (ista adresa u memoriji) potrebna ponovno, procesor prvo provjerava: je li u cacheu? Ako postoji, informacije se preuzimaju od tamo, a pristup memoriji se uopće ne događa. Slično je i s pisanjem: informacije, ako njihov volumen stane u predmemoriju, tamo se zapisuju, a tek onda, kada procesor završi operaciju pisanja i počne izvršavati druge naredbe, podaci se upisuju u predmemoriju. paralelno s radom jezgre procesora“polako istovaruje” u RAM.

Naravno, količina pročitanih i zapisanih podataka tijekom cijelog rada programa puno je veća od veličine predmemorije. Stoga se neke od njih moraju s vremena na vrijeme brisati kako bi nove, relevantnije mogle stati u predmemoriju. Najjednostavniji poznati mehanizam za osiguranje ovog procesa je praćenje vremena zadnjeg pristupa podacima koji se nalaze u predmemorij. Dakle, ako trebamo smjestiti nove podatke u predmemoriju, a ona je već “puna do kraja”, kontroler koji upravlja predmemorijom gleda kojem se fragmentu predmemorije nije pristupalo najdulje vrijeme? Upravo je taj fragment prvi kandidat za “odlazak”, a na njegovom mjestu bilježe se novi podaci s kojima sada treba raditi. Ovo je, općenito govoreći, način na koji funkcionira mehanizam predmemoriranja u procesorima. Naravno, gornje objašnjenje je vrlo primitivno; zapravo, sve je još kompliciranije, ali nadamo se da ste uspjeli dobiti opću ideju o tome zašto procesoru treba predmemorija i kako ona radi.

Da bi bilo jasno koliko je predmemorija važna, navedimo jednostavan primjer: brzina razmjene podataka između procesora Pentium 4 i njegovih predmemorija više je od 10 puta (!) veća od brzine njegovog rada s memorijom. Zapravo, moderni procesori sposobni su punim kapacitetom raditi samo s predmemorijom: čim se suoče s potrebom čitanja podataka iz memorije, svi njihovi hvaljeni megaherci jednostavno počnu "grijati zrak". Opet jednostavan primjer: procesor izvrši najjednostavniju instrukciju u jednom taktu, odnosno u sekundi može izvršiti ovoliko jednostavne upute, koja mu je učestalost (zapravo čak i više, ali to ćemo ostaviti za kasnije...). Ali vrijeme čekanja podataka iz memorije može u najgorem slučaju biti više od 200 ciklusa! Što radi procesor dok čeka potrebne podatke? Ali on ne radi ništa. Samo stojim i čekam...

Predmemoriranje na više razina